### HIGH-SPEED 3.3V 64K x 16 BANK-SWITCHABLE DUAL-PORTED SRAM WITH EXTERNAL BANK SELECTS

#### *IDT70V7288S/L*

#### **Features**

- 64K x 16 Bank-Switchable Dual-Ported SRAM Architecture

- Four independent 16K x 16 banks

- 1 Megabit of memory on chip

- Fast asynchronous address-to-data access time: 15ns

- User-controlled input pins included for bank selects

- Independent port controls with asynchronous address & data busses

- Four 16-bit mailboxes available to each port for interprocessor communications; interrupt option

- Interrupt flags with programmable masking

- Dual Chip Enables allow for depth expansion without external logic

- ◆ UB and LB are available for x8 or x16 bus matching

- ◆ LVTTL-compatible, single 3.3V (±5%) power supply

- Available in a 100-pin Thin Quad Flatpack (14mm x 14mm)

- Industrial temperature range (-40°C to +85°C) is available for selected speeds

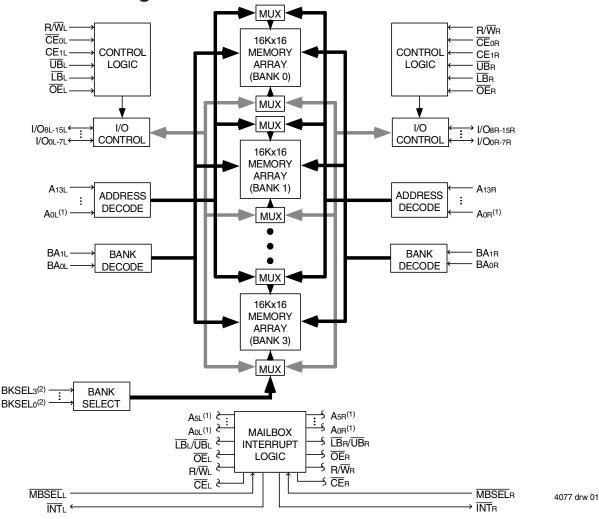

### **Functional Block Diagram**

#### NOTES:

- 1. The first six address pins for each port serve dual functions. When MBSEL = VIH, the pins serve as memory address inputs. When MBSEL = VIL, the pins serve as mailbox address inputs.

- 2. Each bank has an input pin assigned that allows the user to toggle the assignment of that bank between the two ports. Refer to Truth Table I for more details.

**JUNE 2000**

©2000 Integrated Device Technology, Inc. DSC-4077/6

### **Description**

The IDT70V7288 is a high-speed 64K x 16 (1M bit) Bank-Switchable Dual-Ported SRAM organized into four independent 16K x 16 banks. The device has two independent ports with separate controls, addresses, and I/O pins for each port, allowing each port to asynchronously access any 16K x 16 memory block not already accessed by the other port. Accesses by the ports into specific banks are controlled via bank select pin inputs under the user's control. Mailboxes are provided to allow inter-processor communications. Interrupts are provided to indicate mailbox writes have occurred. An automatic power down feature controlled by the chip enables ( $\overline{\text{CE}}\text{o}$  and CE1) permits the onchip circuitry of each port to enter a very low standby power mode and allows fast depth expansion.

The IDT70V7288 offers a maximum address-to-data access time as fast as 15ns, and is packaged in a 100-pin Thin Quad Flatpack (TQFP).

### **Functionality**

The IDT70V7288 is a high-speed asynchronous 64K x 16 Bank-Switchable Dual-Ported SRAM, organized in four 16K x 16 banks. The two ports are permitted independent, simultaneous access into separate banks within the shared array. There are four user-controlled Bank Select input pins, and each of these pins is associated with a specific bank within the memory array. Access to a specific bank is gained by placing the associated Bank Select pin in the appropriate state: VIH assigns the bank to the left port, and VIL assigns the bank to

the right port (See Truth Table IV). Once a bank is assigned to a particular port, the port has full access to read and write within that bank. Each port can be assigned as many banks within the array as needed, up to and including all four banks.

The IDT70V7288 provides mailboxes to allow inter-processor communications. Each port has four 16-bit mailbox registers available to which it can write and read and which the opposite port can read only. These mailboxes are external to the common SRAM array, and are accessed by setting  $\overline{\text{MBSEL}} = \text{VIL}$  while setting  $\overline{\text{CE}} = \text{VIH}$ . Each mailbox has an associated interrupt: a port can generate an interrupt to the opposite port by writing to the upper byte of any one of its four 16-bit mailboxes. The interrupted port can clear the interrupt by reading the upper byte. This read will not alter the contents of the mailbox.

If desired, any source of interrupt can be independently masked via software. Two registers are provided to permit interpretation of interrupts: the Interrupt Cause Register and the Interrupt Status Register. The Interrupt Cause Register gives the user a snapshot of what has caused the interrupt to be generated - the specific mailbox written to. The information in this register provides post-mask signals: Interrupt sources that have been masked will not be updated. The Interrupt Status Register gives the user the status of all bits that could potentially cause an interrupt regardless of whether they have been masked. Truth Table V gives a detailed explanation of the use of these registers.

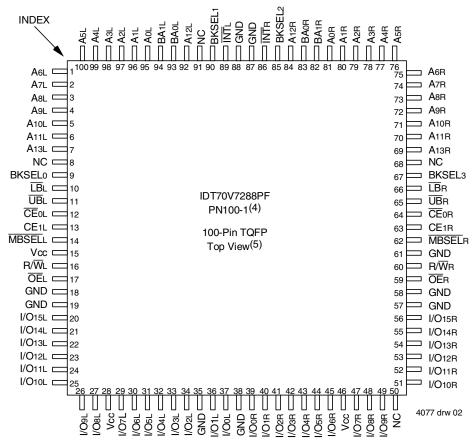

### Pin Configurations<sup>(1,2,3)</sup>

#### NOTES:

- 1. All Vcc pins must be connected to power supply.

- 2. All GND pins must be connected to ground supply.

- 3. Package body is approximately 14mm x 14mm x 1.4mm.

- 4. This package code is used to reference the package diagram.

- 5. This text does not indicate orientation of the actual part-marking.

#### **Pin Names**

| A0 - A13 <sup>(1,6)</sup>               | Address Inputs                         |

|-----------------------------------------|----------------------------------------|

| BA0 - BA1 <sup>(1)</sup>                | Bank Address Inputs                    |

| MBSEL <sup>(1)</sup>                    | Mailbox Access Control Gate            |

| BKSEL <sub>0-3</sub> <sup>(2)</sup>     | Bank Select Inputs                     |

| $R/\overline{W}^{(1)}$                  | Read/Write Enable                      |

| ŌĒ <sup>(1)</sup>                       | Output Enable                          |

| <u>CE</u> ₀, CE₁ <sup>(1)</sup>         | Chip Enables                           |

| $\overline{UB}$ , $\overline{LB}^{(1)}$ | I/O Byte Enables                       |

| VOo - VO15 <sup>(1)</sup>               | Bidirectional Data Input/Output        |

| ĪNT <sup>(1)</sup>                      | Interrupt Flag (Output) <sup>(3)</sup> |

| Vcc <sup>(4)</sup>                      | 3.3VPower                              |

| GND <sup>(5)</sup>                      | Ground                                 |

4077 tbl 01

- 1. Duplicated per port.

- Each bank has an input pin assigned that allows the user to toggle the assignment of that bank between the two ports. Refer to Truth Table IV for more details.

When changing the bank assignments, accesses of the affected banks must be suspended. Accesses may continue uninterrupted in banks that are not being reallocated.

- 3. Generated upon mailbox access.

- 4. All Vcc pins must be connected to power supply.

- 5. All GND pins must be connected to ground supply.

- 6. The first six address pins (A<sub>0</sub>-A<sub>5</sub>) for each port serve dual functions. When MBSEL = V<sub>IH</sub>, the pins serve as memory address inputs. When MBSEL = V<sub>IL</sub>, the pins serve as mailbox address inputs (A<sub>6</sub>-A<sub>13</sub> ignored).

### Truth Table I – Chip Enable<sup>(1,2,3,4)</sup>

| ζĒ | <u>CE</u> ₀                                       | CE1              | Mode                            |  |  |  |

|----|---------------------------------------------------|------------------|---------------------------------|--|--|--|

|    | VIL                                               | VIH              | Port Selected (TTL Active)      |  |  |  |

| L  | L ≤ 0.2V ≥Vcc -0.2V Port Selected (CMOS Active)   |                  |                                 |  |  |  |

|    | V <sub>I</sub> H X Port Deselected (TTL Inactive) |                  |                                 |  |  |  |

| Н  | X                                                 | VIL              | Port Deselected (TTL Inactive)  |  |  |  |

|    | ≥Vcc -0.2V                                        | X                | Port Deselected (CMOS Inactive) |  |  |  |

|    | X                                                 | <u>&lt;</u> 0.2V | Port Deselected (CMOS Inactive) |  |  |  |

#### NOTES:

4077 tbl 02

- 1. Chip Enable references are shown above with the actual  $\overline{\text{CE}}_0$  and  $\text{CE}_1$  levels,  $\overline{\text{CE}}$  is a reference only.

- 2. Port "A" and "B" references are located where  $\overline{\text{CE}}$  is used.

- "H" = VIH and "L" = VIL. 3.

- CE and MBSEL cannot be active at the same time.

#### Truth Table II - Non-Contention Read/Write Control

|                   |     | Inpu | uts <sup>(1)</sup> |    |                  | Outputs |                    |                          |

|-------------------|-----|------|--------------------|----|------------------|---------|--------------------|--------------------------|

| ŒE <sup>(2)</sup> | R/W | Œ    | ŪB                 | ĽΒ | MBSEL            | I/O8-15 | I/O <sub>0-7</sub> | Mode                     |

| Н                 | Х   | Х    | Х                  | Χ  | Н                | High-Z  | High-Z             | Deselected: Power-Down   |

| X <sup>(3)</sup>  | Х   | Х    | Н                  | Н  | X <sup>(3)</sup> | High-Z  | High-Z             | Both Bytes Deselected    |

| L                 | L   | Х    | L                  | Н  | Н                | DATAIN  | High-Z             | Write to Upper Byte Only |

| L                 | L   | Х    | Н                  | L  | Н                | High-Z  | DATAIN             | Write to Lower Byte Only |

| L                 | L   | Х    | L                  | L  | Н                | DATAIN  | DATAIN             | Write to Both Bytes      |

| L                 | Н   | L    | L                  | Н  | Н                | DATAout | High-Z             | Read Upper Byte Only     |

| L                 | Н   | L    | Н                  | L  | Н                | High-Z  | DATAout            | Read Lower Byte Only     |

| L                 | Н   | L    | L                  | L  | Н                | DATAout | DATAout            | Read Both Bytes          |

| X <sup>(3)</sup>  | Х   | Н    | Х                  | Χ  | X <sub>(3)</sub> | High-Z  | High-Z             | Outputs Disabled         |

#### NOTES:

4077 tbl 03

- 1.  $BAOL BAIL \neq BAOR BAIR$ : cannot access same bank simultaneously from both ports.

- 2. Refer to Truth Table I.

- 3.  $\overline{\text{CE}}$  and  $\overline{\text{MBSEL}}$  cannot both be active at the same time.

### Truth Table III - Mailbox Read/Write Control<sup>(1)</sup>

| Inputs |     |    |                  |                  |       | Outputs             |                    |                                           |

|--------|-----|----|------------------|------------------|-------|---------------------|--------------------|-------------------------------------------|

| CE(2)  | R/W | ŌĒ | ŪB               | ĪΒ               | MBSEL | I/O <sub>8-15</sub> | I/O <sub>0-7</sub> | Mode                                      |

| Н      | Н   | L  | X <sup>(3)</sup> | X <sup>(3)</sup> | L     | DATAout             | DATAout            | Read Data from Mailbox, ↓clears interrupt |

| Н      | Н   | L  | L                | L                | L     | <b>DATA</b> out     | DATAout            | Read Data from Mailbox, ↓clears interrupt |

| Н      | L   | Χ  | L <sup>(3)</sup> | L <sup>(3)</sup> | L     | DATAIN              | DATAIN             | Write Data into Mailbox                   |

| L      | Х   | Χ  | Χ                | Х                | L     | _                   | _                  | Not Allowed                               |

#### NOTES:

4077 tbl 04

- 1. There are four mailbox locations per port written to and read from all the I/O's (I/Oo-I/O15). These four mailboxes are addressed by Ao-A5. Refer to Truth Table V.

- Refer to Truth Table I.

- 3. Each mailbox location contains a 16-bit word, controllable in bytes by setting input levels to UB and LB appropriately.

### **Absolute Maximum Ratings**(1)

| Symbol               | Rating                                     | Commercial<br>& Industrial | Unit |

|----------------------|--------------------------------------------|----------------------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +4.6               | V    |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125                | °C   |

| Tstg                 | Storage<br>Temperature                     | -65 to +150                | °C   |

| Іоит                 | DC Output<br>Current                       | 50                         | mA   |

4077 tbl 05 NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VTERM must not exceed Vcc + 5% for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq 20$ mA for the period of VTERM  $\geq V$ CC + 5%.

### Capacitance<sup>(1)</sup>

#### (TA = +25°C, f = 1.0mhz) TQFP Package

| Symbol              | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit |

|---------------------|--------------------|---------------------------|------|------|

| CIN                 | Input Capacitance  | VIN = 3dV                 | 9    | pF   |

| Соит <sup>(3)</sup> | Output Capacitance | Vout = 3dV                | 10   | pF   |

4077 tbl 08 NOTES:

- 1. This parameter is determined by device characterization but is not production

- 2. 3dV represents the interpolated capacitance when the input and output signals switch from 0V to 3V or from 3V to 0V.

- 3. Cout represents Ci/o as well.

### **Maximum Operating Temperature** and Supply Voltage(1)

|            | <b>J</b>               |     |                  |

|------------|------------------------|-----|------------------|

| Grade      | Ambient<br>Temperature | GND | Vcc              |

| Commercial | 0°C to +70°C           | 0V  | 3.3V <u>+</u> 5% |

| Industrial | -40°C to +85°C         | 0V  | 3.3V <u>+</u> 5% |

4077 thl 06

1. This is the parameter Ta. This is the "instant on" case temperature.

### **Recommended DC Operating** Conditions

| Symbol | Parameter          | Min.                | Тур. | Мах.                   | Unit |

|--------|--------------------|---------------------|------|------------------------|------|

| Vcc    | Supply Voltage     | 3.135               | 3.3  | 3.465                  | ٧    |

| GND    | Ground             | 0                   | 0    | 0                      | ٧    |

| VIH    | Input High Voltage | 2.0                 | _    | VCC +5% <sup>(2)</sup> | ٧    |

| VIL    | Input Low Voltage  | -0.3 <sup>(1)</sup> | _    | 0.8                    | ٧    |

#### NOTES:

4077 tbl 07

- 1.  $VIL \ge -1.5V$  for pulse width less than 10ns.

- 2. VTERM must not exceed Vcc + 5%.

### **DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (Vcc = 3.3V ± 5%)**

|        |                                      |                                                                                                     | 70V7288S |      | 70V7 |      |      |

|--------|--------------------------------------|-----------------------------------------------------------------------------------------------------|----------|------|------|------|------|

| Symbol | Parameter                            | Test Conditions                                                                                     | Min.     | Max. | Min. | Max. | Unit |

| Iu     | Input Leakage Current <sup>(1)</sup> | Vcc = 3.465V, $Vin = 0V$ to $Vcc$                                                                   | _        | 10   | -    | 5    | μA   |

| ILO    | Output Leakage Current               | $\overline{\text{CE}} = \text{ViH, } \overline{\text{MBSEL}} = \text{ViH, Vout} = \text{0V to Vcc}$ | _        | 10   | -    | 5    | μΑ   |

| Vol    | Output Low Voltage                   | IoL = +4mA                                                                                          | _        | 0.4  | -    | 0.4  | V    |

| Vон    | Output High Voltage                  | Iон = -4mA                                                                                          | 2.4      | _    | 2.4  | _    | ٧    |

NOTE:

4077 tbl 09

1. At  $Vcc \le 2.0V$ , input leakages are undefined.

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range $^{(1,6)}$ (vcc = 3.3v ± 5%)

|               | Parameter Test Condition                            |                                                                                                                                                                                                                                                                                        |       |        | 70V72<br>Com'l      |            | 70V72<br>Com'l      |            | 70V72<br>Com'l      |            |      |

|---------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|---------------------|------------|---------------------|------------|---------------------|------------|------|

| Symbol        |                                                     |                                                                                                                                                                                                                                                                                        | Versi | on     | Typ. <sup>(2)</sup> | Max.       | Typ. <sup>(2)</sup> | Max.       | Typ. <sup>(2)</sup> | Max.       | Unit |

| Icc           | Dynamic Operating<br>Current<br>(Both Ports Active) | $\overline{CE}$ = V <sub>IL</sub> , Outputs Disabled<br>$\overline{MBSEL}$ = V <sub>IH</sub><br>$f$ = $fMAX^{(3)}$                                                                                                                                                                     | COM'L | S<br>L | 200<br>200          | 280<br>230 | 170<br>170          | 260<br>210 | 160<br>160          | 250<br>200 | mA   |

|               | (BUIT POILS ACTIVE)                                 | T = IMAX <sup>©</sup> /                                                                                                                                                                                                                                                                | IND   | S<br>L |                     |            |                     |            | 160<br>160          | 280<br>230 |      |

| ISB1          | Standby Current<br>(Both Ports - TTL Level          | CEL = CER = VIH<br>MBSELR = MBSELL = VIH                                                                                                                                                                                                                                               | COM'L | S<br>L | 50<br>50            | 85<br>60   | 40<br>40            | 75<br>50   | 35<br>35            | 70<br>45   | mA   |

|               | Inputs)                                             | $f = fMAX^{(3)}$                                                                                                                                                                                                                                                                       | IND   | S<br>L |                     | 1 1        | 1 1                 |            | 35<br>35            | 80<br>55   |      |

| ISB2          | (One Port - TTL Level                               | \[       \overline{OE}^*A" = VIL and \(       \overline{CE}^*B" = VIH^{(5)}       \]       Active Port Outputs Disabled, f=fMaX^(5)       \[       \overline{MBSELR} = \overline{MBSELL} = VIH       \]                                                                                | COM'L | S<br>L | 120<br>120          | 160<br>140 | 100<br>100          | 140<br>120 | 90<br>90            | 130<br>110 | mA   |

|               | Inputs)                                             |                                                                                                                                                                                                                                                                                        | IND   | S<br>L |                     |            |                     |            | 90<br>90            | 150<br>130 |      |

| ISB3          | Full Standby Current<br>(Both Ports - All CMOS      | Both Ports CEL and<br>CER > VCC - 0.2V<br>VIN > VCC - 0.2V or                                                                                                                                                                                                                          | COM'L | S<br>L | 1.5<br>1.5          | 6<br>3     | 1.5<br>1.5          | 6<br>3     | 1.5<br>1.5          | 6<br>3     | mA   |

| Level Inputs) | Level inpuis)                                       | $\frac{VIN \ge VCC - 0.2V \text{ of }}{VIN \le 0.2V, f = 0^{(4)}}$ $\overline{MBSELR} = \overline{MBSELL} \ge VCC - 0.2V$                                                                                                                                                              | IND   | S<br>L |                     | 11         | 1 1                 | 1 1        | 1.5<br>1.5          | 10<br>6    |      |

| ISB4          | Full Standby Current<br>(One Port - All CMOS        | $\overline{CE}^*A^* \leq 0.2V$ and $\overline{CE}^*B^* \geq VCC - 0.2V^{(5)}$                                                                                                                                                                                                          | COM'L | S<br>L | 115<br>115          | 140<br>125 | 95<br>95            | 130<br>110 | 85<br>85            | 120<br>100 | mA   |

|               | Level Inputs)                                       | $\begin{array}{ll} \overline{\text{MBSELR}} = \overline{\text{MBSELL}} \geq \text{VCC} - 0.2\text{V} \\ \overline{\text{VIN}} \geq \text{VCC} - 0.2\text{V or } \overline{\text{VIN}} \leq 0.2\text{V} \\ \text{Active Port Outputs Disabled} \\ f = f_{\text{MAX}}^{(8)} \end{array}$ |       | S<br>L |                     |            | _                   | _          | 85<br>85            | 140<br>120 |      |

#### 4077 tbl 10

- 1. 'X' in part numbers indicates power rating (S or L).

- 2. Vcc = 3.3V, TA = +25°C, and are not production tested. Icccc = 120mA (Typ.)

- 3. At f = fmax, address and control lines (except Output Enable) are cycling at the maximum frequency read cycle of 1 / tRc, and using "AC Test Conditions" of input levels of GND to 3V.

- 4. f = 0 means no address or control lines change.

- 5. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- 6. Refer to Truth Table I.

#### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise/Fall Times         | 3ns Max.          |

| Input Timing Reference Levels | 1.5V              |

| Output Reference Levels       | 1.5V              |

| Output Load                   | Figures 1,2 and 3 |

4077 tbl 11

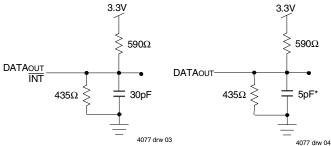

Figure 1. AC Output Test Load

Figure 2. Output Test Load (for tLz, tHz, twz, tow) \*Including scope and jig.

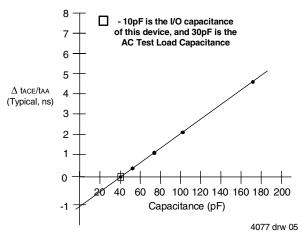

Figure 3. Lumped Capacitance Load Typical Derating Curve

### **AC Electrical Characteristics Over the** Operating Temperature and Supply Voltage Range<sup>(4)</sup>

|            |                                                  |      | 88X15<br>Only | 70V7288X20<br>Com'l Only |      | 70V7288X25<br>Com'l & Ind |      |      |  |

|------------|--------------------------------------------------|------|---------------|--------------------------|------|---------------------------|------|------|--|

| Symbol     | Parameter                                        | Min. | Max.          | Min.                     | Max. | Min.                      | Max. | Unit |  |

| READ CYCLE | •                                                |      |               |                          |      |                           |      |      |  |

| trc        | Read Cycle Time                                  | 15   |               | 20                       |      | 25                        | _    | ns   |  |

| taa        | Address Access Time                              |      | 15            | _                        | 20   | _                         | 25   | ns   |  |

| tace       | Chip Enable Access Time <sup>(3)</sup>           | _    | 15            | _                        | 20   | _                         | 25   | ns   |  |

| tabe       | Byte Enable Access Time <sup>(3)</sup>           | _    | 15            | _                        | 20   | _                         | 25   | ns   |  |

| taoe       | Output Enable Access Time                        | _    | 9             | _                        | 10   | _                         | 11   | ns   |  |

| tон        | Output Hold from Address Change                  | 3    | _             | 3                        |      | 3                         |      | ns   |  |

| tLZ        | Output Low-Z Time <sup>(1,2)</sup>               | 0    | _             | 0                        | _    | 0                         | _    | ns   |  |

| tHZ        | Output High-Z Time <sup>(1,2)</sup>              |      | 8             | _                        | 9    | _                         | 10   | ns   |  |

| tpu        | Chip Enable to Power Up Time (2.5)               | 0    | _             | 0                        |      | 0                         |      | ns   |  |

| tpd        | Chip Disable to Power Down Time <sup>(2,5)</sup> |      | 15            | _                        | 20   | _                         | 25   | ns   |  |

| тмор       | Mailbox Flag Update Pulse (OE or MBSEL)          | 10   | _             | 10                       |      | 10                        |      | ns   |  |

| tmaa       | Mailbox Address Access Time                      |      | 15            | _                        | 20   | _                         | 25   | ns   |  |

- Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

- This parameter is guaranteed by device characterization, but is not production tested.

- To access RAM,  $\overline{CE}$  = VIL and  $\overline{MBSEL}$  = VIH. To access mailbox,  $\overline{CE}$  = VIH and  $\overline{MBSEL}$  = VIL.

- 'X' in part numbers indicates power rating (S or L).

- 5. Refer to Truth Table I.

### Assigning the Banks via the External Bank Selects

There are four bank select pins available on the IDT70V7288, and each of these pins is associated with a specific bank within the memory array. The pins are user-controlled inputs: access to a specific bank is assigned to a particular port by setting the input to the appropriate level. The process of assigning the banks is detailed in Truth Table IV. Once a bank is assigned to a port, the owning port has full access to read and write within that bank. The opposite port is unable to access that bank until the user reassigns the port. Access by a port to a bank

which it does not control will have no effect if written, and if read unknown values on Do-D15 will be returned. Each port can be assigned as many banks within the array as needed, up to and including all four banks.

The bank select pin inputs must be set at either VIH or VIL - these inputs are not tri-statable. When changing the bank assignments, accesses of the affected banks must be suspended. Accesses may continue uninterrupted in banks that are not being reallocated.

Truth Table I<u>V</u> – Memory Bank Assignment (CE = Vін)<sup>(2,3)</sup>

| BKSEL0 | BKSEL1 | BKSEL2 | BKSEL3 | BANK AND<br>DIRECTION <sup>(1)</sup> |

|--------|--------|--------|--------|--------------------------------------|

| Н      | Х      | Х      | Х      | BANK 0 LEFT                          |

| Х      | Н      | Х      | Х      | BANK 1 LEFT                          |

| Х      | Х      | Н      | Х      | BANK 2 LEFT                          |

| Х      | Х      | Х      | Н      | BANK 3 LEFT                          |

| L      | Х      | Х      | Х      | BANK 0 RIGHT                         |

| Х      | L      | Х      | Х      | BANK 1 RIGHT                         |

| Х      | Х      | L      | Х      | BANK 2 RIGHT                         |

| Х      | Х      | Х      | L      | BANK 3 RIGHT                         |

**NOTES:** 4077 tbl 13

- Bank 0 refers to the first 16Kx16 memory spaces, Bank 1 to the second 16Kx16 memory spaces, Bank 2 to the third 16Kx16 memory spaces; and Bank 3 to the fourth 16Kx16 memory spaces. 'LEFT' indicates the bank is assigned to the left port; 'RIGHT' indicates the bank is assigned to the right port. 0-4 banks may be assigned to either port.

- The bank select pin inputs must be set at either VIH or VIL these inputs are not tristatable. When changing the bank assignments, accesses of the affected banks must be suspended. Accesses may continue uninterrupted in banks that are not being reallocated.

- 3.  $'H' = V_{IH}$ ,  $'L' = V_{IL}$ , 'X' = Don't Care.

### Mailbox Interrupts and Interrupt Control Registers

If the user chooses the mailbox interrupt function, four mailbox locations are assigned to each port. These mailbox locations are external to the memory array. The mailboxes are accessed by taking  $\overline{\text{MBSEL}}$  LOW while holding  $\overline{\text{CE}}$  HIGH.

The mailboxes are 16 bits wide and controllable by byte: the message is user-defined since these are addressable SRAM locations. An interrupt is generated to the opposite port upon writing to the upper byte of any mailbox location. A port can read the message it has just written in order to verify it: this read will not alter the status of the interrupt sent to the opposite port. The interrupted port can clear the interrupt by reading the upper byte of the applicable mailbox. This read will not alter the contents of the mailbox. The use of mailboxes to generate interrupts to the opposite port and the reading of mailboxes to clear interrupts is detailed in Truth Table V.

If desired, any of the mailbox interrupts can be independently

masked via software. Masking of the interrupt sources is done in the Mask Register. The masks are individual and independent: a port can mask any combination of interrupt sources with no effect on the other sources. Each port can modify only its own Mask Register. The use of this register is detailed in Truth Table V.

Two registers are provided to permit interpretation of interrupts: these are the Interrupt Cause Register and the Interrupt Status Register. The Interrupt Cause Register gives the user a snapshot of what has caused the interrupt to be generated - the specific mailbox written to by the opposite port. The information in this register provides post-mask signals: interrupt sources that have been masked will not be updated. The Interrupt Status Register gives the user the status of all bits that could potentially cause an interrupt regardless of whether they have been masked. The use of the Interrupt Cause Register and the Interrupt Status Register is detailed in Truth Table V.

### Truth Table V – Mailbox Interrupts ( $\overline{CE} = V_{IH}$ )(8,9)

| MB<br>SEL    | R/W | ī <del>UB</del> | ĪΒ  | <b>A</b> 5 | A4 | А3 | A2 | <b>A</b> 1 | A0 | D0           | D1           | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12          | D13 | D14          | D15          | DESCRIPTION                                |

|--------------|-----|-----------------|-----|------------|----|----|----|------------|----|--------------|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------|-----|--------------|--------------|--------------------------------------------|

| L            | Χ   | Х               | Х   | L          | L  | L  | L  | L          | L  | RESERVED (7) |              |     |     |     |     |     |     |     |     |     |     | RESERVED (7) |     |              |              |                                            |

| L            | Х   | Х               | Х   |            | :  | :  | ÷  | ÷          |    | RESERVED (7) |              |     |     |     |     |     |     |     |     |     |     |              |     |              | RESERVED (7) |                                            |

| L            | (1) | (1)             | (1) | Η          | L  | L  | L  | L          | L  | Х            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ            | Χ   | Χ            | Χ            | MAILBOX 0 - SET INTERRUPT ON OPPOSITE PORT |

| L            | (1) | (1)             | (1) | Ξ          | L  | L  | L  | L          | Н  | Х            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Х   | Х            | Х   | Χ            | Χ            | MAILBOX 1 - SET INTERRUPT ON OPPOSITE PORT |

| L            | (1) | (1)             | (1) | Η          | L  | L  | L  | Н          | L  | Х            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ            | Χ   | Χ            | Χ            | MAILBOX 2 - SET INTERRUPT ON OPPOSITE PORT |

| L            | (1) | (1)             | (1) | Η          | L  | L  | L  | Н          | Н  | Х            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ            | Χ   | Χ            | Χ            | MAILBOX 3 - SET INTERRUPT ON OPPOSITE PORT |

| $\downarrow$ | Н   | (2)             | (2) | Η          | L  | L  | Н  | L          | L  | Χ            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ            | Χ   | Χ            | Χ            | MAILBOX 0 - CLEAR OPPOSITE PORT INTERRUPT  |

| $\downarrow$ | Н   | (2)             | (2) | Η          | L  | L  | Н  | L          | Н  | Х            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ            | Χ   | Χ            | Χ            | MAILBOX 1 - CLEAR OPPOSITE PORT INTERRUPT  |

| $\downarrow$ | Н   | (2)             | (2) | Η          | L  | L  | Н  | Н          | L  | Х            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ            | Χ   | Χ            | Χ            | MAILBOX 2 - CLEAR OPPOSITE PORT INTERRUPT  |

| $\downarrow$ | Н   | (2)             | (2) | Н          | L  | L  | Н  | Н          | Н  | Х            | Χ            | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ            | Χ   | Χ            | Χ            | MAILBOX 3 - CLEAR OPPOSITE PORT INTERRUPT  |

| L            | (3) | (3)             | (3) | Ξ          | L  | Н  | L  | L          | L  | (4)          | (4)          | (4) | (4) | (5) | (5) | (5) | (5) | (6) | (6) | (6) | (6) | Χ            | Χ   | Χ            | Χ            | MAILBOX INTERRUPT CONTROLS                 |

| L            | Χ   | Х               | Х   |            | :  | :  | :  | :          | :  | RE           | RESERVED (7) |     |     |     |     |     |     |     |     |     |     |              |     |              |              | RESERVED (7)                               |

| L            | Х   | Х               | Х   | Н          | Н  | Н  | Н  | Н          | Н  | RESERVED (7) |              |     |     |     |     |     |     |     |     |     |     |              |     | RESERVED (7) |              |                                            |

- 1. There are four independent mailbox locations available to each side, external to the standard memory array. The mailboxes can be written to in either 8-bit or 16-bit widths. The upper byte of each mailbox has an associated interrupt to the opposite port. The mailbox interrupts can be individually masked if desired, and the status of the interrupt determined by polling the Interrupt Status Register (see Note 6 for this table). A port can read its own mailboxes to verify the data written, without affecting the interrupt which is sent to the opposite port.

- 2. These registers allow a port to read the data written to a specific mailbox location by the opposite port. Reading the upper byte of the data in a particular mailbox clears the interrupt associated with that mailbox without modifying the data written. Once the address and R/W are stable, the actual clearing of the interrupt is triggered by the transition of MBSEL from VIH to VIL.

- 3. This register contains the Mask Register (bits Do-D<sub>3</sub>), the Interrupt Cause Register (bits D<sub>4</sub>-D<sub>7</sub>), and the Interrupt Status Register (bits D<sub>8</sub>-D<sub>11</sub>). The controls for R/W, UB, and LB are manipulated in accordance with the appropriate function. See Notes 4, 5, and 6 for this table. Bits D12-D15 are "Don't Care".

- 4. This register, the Mask Register, allows the user to independently mask the various interrupt sources. Writing VIH to the appropriate bit (Do = Mailbox 0, D1 = Mailbox 1, D2 = Mailbox 2, and D3 = Mailbox 3) disables the interrupt, while writing VIL enables the interrupt. All four bits in this register must be written at the same time. This register can be read at any time to verify the mask settings. The masks are individual and independent: any single interrupt source can be masked with no effect on the other sources. Each port can modify only its own mask settings.

- 5. This register, the Interrupt Cause Register, gives the user a snapshot of what has caused the interrupt to be generated. Reading Vol. for a specific bit (D4 = Mailbox 0, D5 = Mailbox 1, D<sub>6</sub> = Mailbox 2, and D<sub>7</sub> = Mailbox 3) indicates that the associated interrupt source has generated an interrupt. Acknowledging the interrupt clears the bit in this register (see Note 2 for this table). This register provides post-mask information: if the interrupt source has been masked, the associated bit in this register will not update.

- 6. This register, the Interrupt Status Register, gives the user the status of all interrupt sources that could potentially cause an interrupt regardless of whether they have been masked. Reading Vol. for a specific bit (D8 = Mailbox 0, D9 = Mailbox 1, D10 = Mailbox 2, and D11 = Mailbox 3) indicates that the associated interrupt source has generated an interrupt. Acknowledging the interrupt clears the associated bit in this register (see Note 2 for this table). This register provides pre-mask information: regardless of whether an interrupt source has been masked, the associated bit in this register will update.

- Access to registers defined as "RESERVED" will have no effect, if written, and if read unknown values on Do-D<sub>15</sub> will be returned.

- These registers are not guaranteed to initialize in any known state. At power-up, the initialization sequence should include the set-up of these registers.

- 9. 'L' = VIL or Vol, 'H' = VIH or VoH, 'X' = Don't Care.

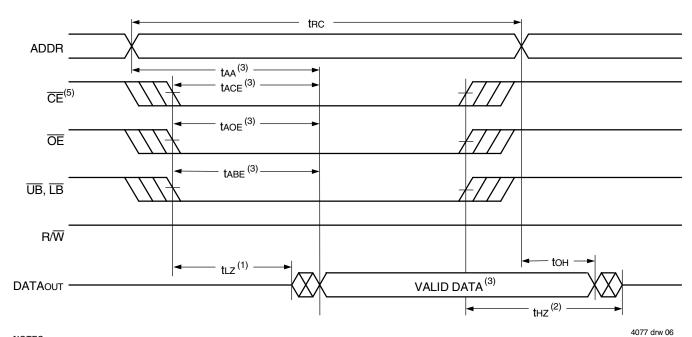

### Waveform of Read Cycles<sup>(4)</sup>

- 1. Timing depends on which signal is asserted last,  $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{LB}$ , or  $\overline{UB}$ .

- 2. Timing depends on which signal is de-asserted first  $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{LB}$ , or  $\overline{UB}$ .

- 3. Start of valid data depends on which timing becomes effective last: taoe, tace, taa or tabe.

- 4.  $\overline{\text{MBSEL}} = \text{ViH}$ .

- 5. Refer to Truth Table I.

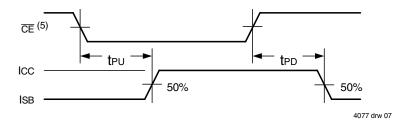

### **Timing of Power-Up Power-Down**

### **AC Electrical Characteristics Over the** Operating Temperature and Supply Voltage<sup>(5)</sup>

|             |                                                    |      | 188X15<br>I Only |      | 88X20<br>I Only | 70V72<br>Com'l |      |      |

|-------------|----------------------------------------------------|------|------------------|------|-----------------|----------------|------|------|

| Symbol      | Parameter                                          | Min. | Max.             | Min. | Max.            | Min.           | Max. | Unit |

| WRITE CYCLE | E                                                  | •    |                  |      |                 |                |      |      |

| twc         | Write Cycle Time                                   | 15   |                  | 20   | _               | 25             | _    | ns   |

| tew         | Chip Enable to End-of-Write <sup>(3)</sup>         | 12   |                  | 15   | _               | 20             | _    | ns   |

| taw         | Address Valid to End-of-Write                      | 12   | _                | 15   | _               | 20             | _    | ns   |

| tas         | Address Set-up Time <sup>(3)</sup>                 | 0    | _                | 0    | _               | 0              | _    | ns   |

| tBS         | Bank Set-up Time                                   | 0    | _                | 0    | _               | 0              | _    | ns   |

| twp         | Write Pulse Width                                  | 12   | _                | 15   | _               | 20             | _    | ns   |

| twr         | Write Recovery Time                                | 0    | _                | 0    | _               | 0              | _    | ns   |

| tow         | Data Valid to End-of-Write                         | 12   | _                | 15   | _               | 20             | _    | ns   |

| tHZ         | Output High-Z Time <sup>(1,2)</sup>                | _    | 8                |      | 9               | _              | 10   | ns   |

| tон         | Data Hold Time <sup>(4)</sup>                      | 0    |                  | 0    | _               | 0              | _    | ns   |

| twz         | Write Enable to Output in High-Z <sup>(1,2)</sup>  |      | 8                |      | 9               |                | 10   | ns   |

| tow         | Output Active from End-of-Write <sup>(1,2,4)</sup> | 3    | _                | 3    | _               | 3              | _    | ns   |

| tmwrd       | Mailbox Write to Read Time                         | 5    | _                | 5    | _               | 5              | _    | ns   |

4077 tbl 15 NOTES:

- 1. Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

- This parameter is guaranteed by device characterization, but is not production tested.

To access RAM, CE = VIL and MBSEL = VIH. To access mailbox, CE = VIH and MBSEL = VIL. Either condition must be valid for the entire tew time. Refer to Truth Tables I and III.

- 4. The specification for tbH must be met by the device supplying write data to the RAM under all operating conditions. Although tbH and tow values will vary over voltage and temperature, the actual ton will always be smaller than the actual tow.

- 5. 'X' in part numbers indicates power rating (S or L).

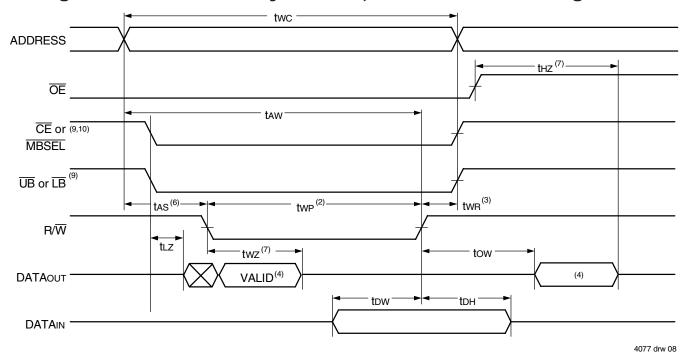

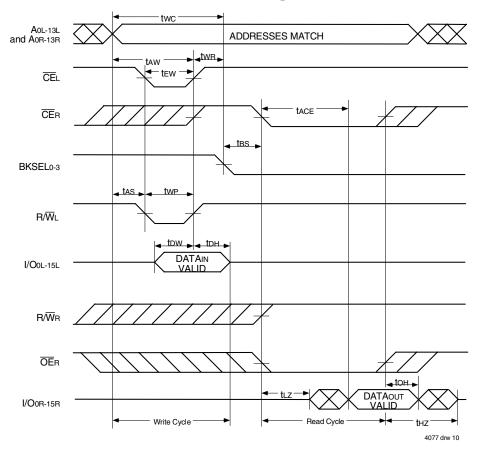

## Timing Waveform of Write Cycle No. 1, $R/\overline{W}$ Controlled Timing<sup>(1,5,8)</sup>

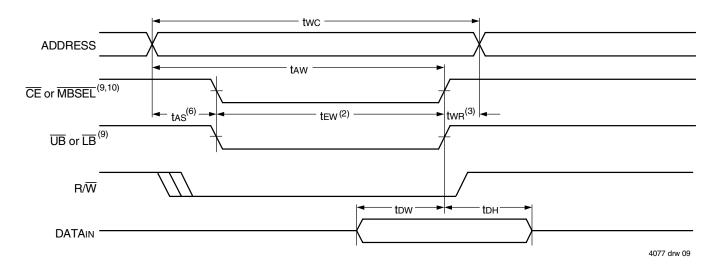

### Timing Waveform of Write Cycle No. 2, $\overline{\text{CE}}$ , $\overline{\text{UB}}$ , $\overline{\text{LB}}$ Controlled Timing<sup>(1,5)</sup>

- 1.  $R/\overline{W}$  or  $\overline{CE}$  or  $\overline{UB}$  and  $\overline{LB}$  must be HIGH during all address transitions.

- 2. A write occurs during the overlap (tew or twp) of a LOW  $\overline{\text{CE}}$  and a LOW R/ $\overline{\text{W}}$  for memory array writing cycle.

- 3. twn is measured from the earlier of  $\overline{\text{CE}}$  or  $R/\overline{W}$  (or  $\overline{\text{MBSEL}}$  or  $R/\overline{W}$ ) going HIGH to the end of write cycle.

- 4. During this period, the I/O pins are in the output state and input signals must not be applied.

- 5. If the CE or MBSEL LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the High-impedance state.

- Timing depends on which enable signal is asserted last,  $\overline{CE}$  or  $R/\overline{W}$ .

- This parameter is guaranteed by device characterization, but is not production tested. Transition is measured 0mV from steady state with the Output Test Load

- If  $\overrightarrow{OE}$  is LOW during R/W controlled write cycle, the write pulse width must be the larger of two or (twz + tow) to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If  $\overline{OE}$  is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

- To access RAM,  $\overline{CE} = VIL$  and  $\overline{MBSEL} = VIH$ . To access mailboxes,  $\overline{CE} = VIH$  and  $\overline{MBSEL} = VIL$ . LEW must be met for either condition.

- 10. Refer to Truth Table I.

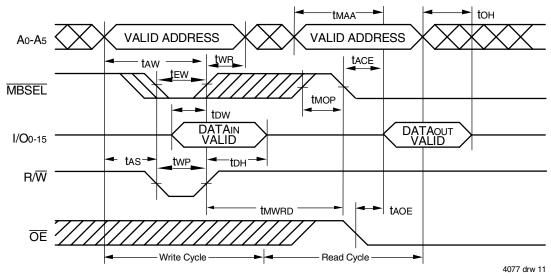

## Timing Waveform of Left Port Write to Right Port Read of Same Data<sup>(1,2,3)</sup>

#### NOTES:

- 1.  $\overline{\text{UB}}$  and  $\overline{\text{LB}}$  are controlled as necessary to enable the desired byte accesses.

- 2. Timing for Right Port Write to Left Port Read is identical.

- Refer to Truth Tables I and IV.

### Timing Waveform of Mailbox Read after Write Timing, Either Side<sup>(1,2)</sup>

- 1.  $\overline{CE}$  = VIH for the duration of the above timing (both write and read cycle), refer to Truth Table I.

- 2. UB and LB are controlled as necessary to enable the desired byte accesses.

4077 tbl 16

### **AC Electrical Characteristics Over the** Operating Temperature and Supply Voltage Range<sup>(1)</sup>

| _           |                      |      | 288X15<br>'I Only |      | 288X20<br>'I Only | 70V72<br>Com'l |      |      |

|-------------|----------------------|------|-------------------|------|-------------------|----------------|------|------|

| Symbol      | Parameter            | Min. | Max.              | Min. | Max.              | Min.           | Max. | Unit |

| INTERRUPT T | IMING                |      |                   |      |                   |                |      |      |

| tas         | Address Set-up Time  | 0    | _                 | 0    | _                 | 0              | _    | ns   |

| twr         | Write Recovery Time  | 0    | _                 | 0    | _                 | 0              | _    | ns   |

| tins        | Interrupt Set Time   | _    | 15                | _    | 20                | _              | 25   | ns   |

| tinr        | Interrupt Reset Time | _    | 15                | _    | 20                | _              | 25   | ns   |

#### NOTES:

1. 'X' in part numbers indicates power rating (S or L).

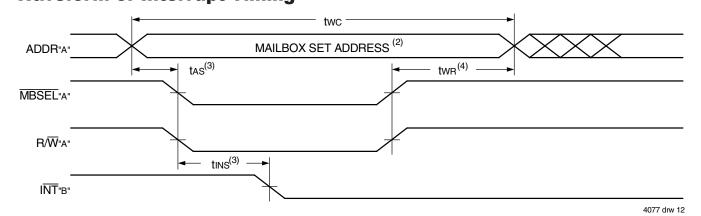

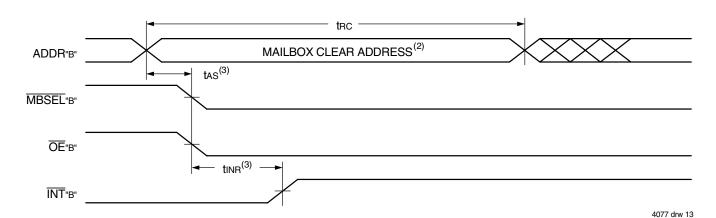

# **Waveform of Interrupt Timing**<sup>(1,5)</sup>

- 1. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from port "A".

- See Interrupt Truth Table V.

- 3. Timing depends on which enable signal ( $\overline{\text{CE}}$  or  $\overline{\text{R/W}}$ ) is asserted last.

- 4. Timing depends on which enable signal (CE or R/W) is de-asserted first.

- 5. Refer to Truth Tables I.

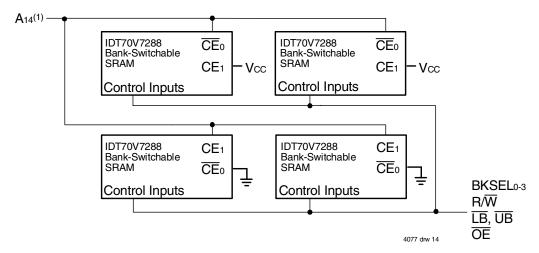

### **Depth and Width Expansion**

The IDT70V7288 features dual chip enables (refer to Truth Table I) in order to facilitate rapid and simple depth expansion with no requirements for external logic. Figure 4 illustrates how to control the various chip enables in order to expand two devices in depth.

The IDT70V7288 can also be used in applications requiring

expanded width, as indicated in Figure 4. Since the banks are allocated at the discretion of the user, the external controller can be set up to drive the input signals for the various devices as required to allow for 32-bit or wider applications.

Figure 4. Depth and Width Expansion with IDT70V7288

#### NOTE:

1. This signal is provided by external logic. It is not a bit present on the address bus.

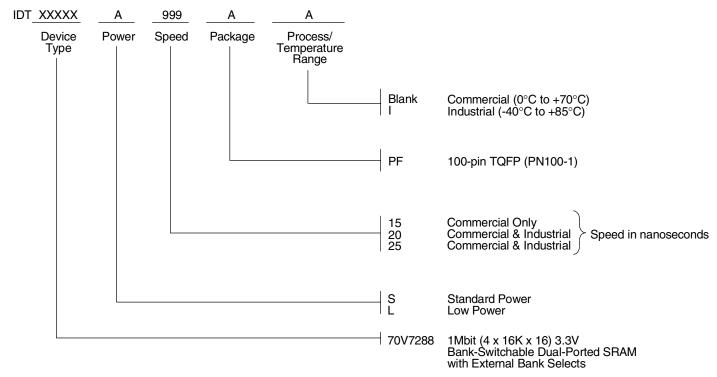

### **Ordering Information**

4077 drw 15

### **Datasheet Document History**

3/8/99: Initiated datasheet document history

Converted to new format

Cosmetic typographical corrections

Page 3 Added additional notes to pin configurations

Added 15ns speed grade

6/11/99: Changed drawing format 9/1/99: Removed Preliminary

3/10/00: Added Industrial Temperature Ranges and removed corresponding notes

Replaced IDT logo

Page 1 Added industrial temperature note Changed ±200mV to 0mV in notes

6/8/00: Page 5 Increated storage temperature parameter

Clarified TA Parameter

Page 6 DC Electrical parameters—changed wording from "open" to "disabled"

CORPORATE HEADQUARTERS

6024 Silver Creek Valley Road

San Jose, CA 95138

for SALES:

800-345-7015 or 408-284-8200

fax: 408-284-2775

www.idt.com

for Tech Support: 408-284-2794 DualPortHelp@idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.